(사진=SK하이닉스)

(사진=SK하이닉스)

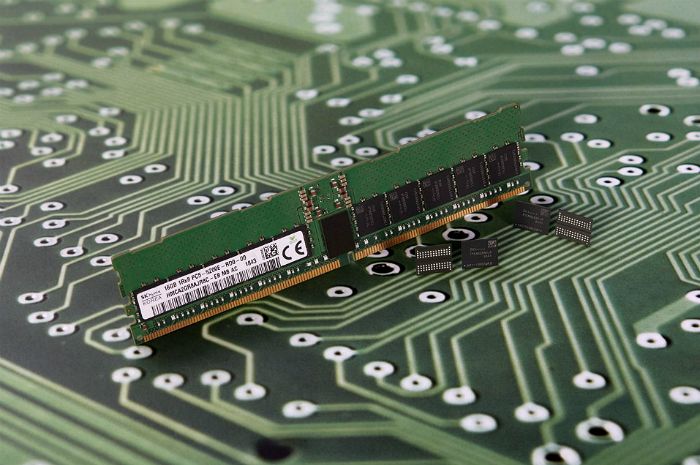

세계 D램 반도체 시장에서 삼성전자에 이어 부동의 2위인 SK하이닉스가 차세대 D램과 4D 낸드 등에서 잇따라 세계 최초 제품을 개발하면서 반도체 시장 지배력을 높여가겠다는 뜻을 분명히 하고 있다.

SK하이닉스는 최근 세계 최초로 JEDEC 즉 국제반도체표준협의기구 규격을 적용한 DDR5 D램을 개발했다고 밝혔다.

모바일용으로 쓰이는 DDR5 D램은 이미 삼성전자가 발표했지만 서버용이나 PC용으로 쓰이는 DDR5 D램 개발은 하이닉스가 처음이다.

DDR5는 현재 상용화되는 D램의 주종을 이루는 DDR4를 잇는 차세대 D램 표준규격으로 빅데이터나 인공지능, 머신러닝 등 차세대 시스템에 최적화된 초고속, 저전력, 고용량 제품이다.

SK하이닉스는 최근 개발한 2세대 10나노급(1y) 8Gbit(기가비트) DDR4에 이어, 동일한 미세공정을 적용한 16Gbit DDR5도 양산하기 위한 개발을 완료했다.

칩의 크기를 더 작게 만들어 전력소모가 30% 감소하고 속도는 1.6배 빨라져 풀HD급 영화 11편을 단 1초에 처리할 수 있다고 하이닉스는 소개했다.

SK하이닉스는 내후년인 2020년부터는 현재 D램의 대표격인 DDR4 D램이 DDR5로 바뀔 것으로 보고 선제적으로 개발을 완료했다고 밝혔다.

하이닉스는 시장조사기관 IDC가 DDR5 수요가 2020년부터 본격적으로 발생하기 시작해 2021년에는 전체 D램 시장의 25%, 2022년에는 44%로 지속 확대될 것으로 전망했다고 전했다.

SK하이닉스는 앞서 낸드 메모리에서도 현재 주종을 이루는 3D를 넘어서는 4D 낸드를 세계 최초로 개발했다고 밝혔다.

3D는 정보가 저장되는 셀을 위아래로 쎃는 적층방식으로 만들고 셀간 정보전달을 위한 공간 즉 페리(PERI)를 적층된 셀 옆에 두는 방식을 채택하고 있다.

고층빌딩을 지어 층수를 높이되 주차장은 빌딩옆 공터에 넑게 짓는 방식이다.

(사진=SK하이닉스)

(사진=SK하이닉스)

그런데 SK하이닉스가 개발했다는 4D 낸드는 지상주차공간을 빌딩 지하로 옮기는 형태이다. 즉 PUC(Peri Under Cel) 방식이다.

이런 방식은 일종의 지하주차장을 파는 공정이 하나 더 들어가기는 하지만 각 칩의 사이즈를 더 작게 만들 수 있는 장점이 있다고 하이닉스 측은 설명했다.

하이닉스는 이렇게 할 경우 72단 512Gbit 3D 낸드보다 칩(Chip) 사이즈는 30% 이상 줄었고, 웨이퍼(Wafer)당 비트(bit) 생산은 1.5배 증가했다고 전했다.

이 제조방법은 대부분의 낸드메모리 업체가 사용하는 3D와 비교해 4D로 명명됐고 아직 일반화 되지는 않았지만 하이닉스는 이 방식이 확산될 것으로 보고 있다.

올들어 3분기까지 영업이익 22조로 사상 최고기록을 쓰고 있는 SK하이닉스가 잇단 신기술을 선보이면서 반도체 시장 지배력 강화를 추구하고 있다.